Tuesday, December 30, 2008

Where the Hell is Matt?

他在2003年用他所有的積蓄去旅行,

在旅行中只是一個簡單的想法,用跳舞記錄他到過的每個地方,

而他都把所有的紀錄放在自己的網站,

當初網站也只是要讓他的親人與朋友知道他在外一切安好。

後來有人發現了這些影片並開始傳閱,

於是有家口香糖廠商覺得他的構想很棒,贊助他旅遊經費,

因此在2006年他花了六個月走遍了39個國家,

接下來的2007、2008年他依舊到世界各地跳舞(包括了台灣),

而且還有了許多的同伴共舞。

Matt跳的舞很滑稽,但是他的笑容與熱情卻是讓人感動,

他只是一個簡單的動作、簡單的想法改變了他的一生,

至今他已經去了63個國家!

有時想想我們是不是都有認真的看待我們靈機一動的小想法?

我們是不是真的就去執行了?還是我們會因為旁人的取笑就做罷了?

如果我們都像Matt這樣認真對待一個這麼簡單、或許說很呆的想法,

或許一個無法預期的驚喜就等著我們!

就算我們得不到相同的驚喜,至少我們擁有了年老了值得回憶的豐富生命!

這一直是我追尋的目標!

我期待我年老了,回頭看我所有的每一步,

我都可以很感謝我給了自己每一個微笑、大笑的回憶,

而不是一直說:「早知道我那時就應該做....」,

我可以很自豪的說:「Blue的生命是精彩豐富的!」

來台灣時,大概沒有幾個人知道他

所以只有孤單的一個人跳囉

Monday, December 29, 2008

點餐機器人可以招呼引導客人上桌點餐

點餐機器人可以招呼引導客人上桌點餐

中廣新聞網 / 張文祿 2008/12/29

日本在機器人研發已經有很好的成果,而國內也有一群人默默投注心力,勤益科技大學電子系今天發表研發成果,展示十部機器人,其中,點餐服務機器人,可以用口語跟客人打招呼,並引導客人就定位,未來還將擬人化,將外型修改成人型,不過,由於造價仍高,要實際運用在餐廳,仍有一段距離。

(張文祿報導) 這部點餐服務機器人,身高一百五十公分,勤益科大電子系黃國興教授帶領四名同學以一年時間完成,這部機器人有臉部辨識系統,有客人上門,他就會主動打招呼,機器人會查看哪裡有空位,規劃最佳路徑,帶領客人到達指定桌號,再透過觸控、聲控的方式進行點餐,並將點好的菜單利用無線網路傳送到櫃檯、廚房。黃國興教授說,未來第二代機器人,外型將更接近人形,並裝上可實際操作的電子手臂。

黃國興表示,未來此款機器人可達到以影像辨識主人的功能,認知主人並跟隨主人走,至室外則以KGPS即時動態全球衛星定位導航系統,執行定位導航的功能,達到公分級的定位。

除此之外,還有撿網球機器人、用面具聲即可聲控的變型金剛和會偵測地板骯髒程度決定吸力大小的「智慧型模糊吸塵器」。黃國興教授表示,未來會將兩輪自平衡及兩隻五軸機械手臂加入半人型機器人的計劃中,使機器人更擬人化並可做其他更復雜的工作。

這部機器人因為造價高達一百四十萬元,要實際在餐廳運用,可能還有一段距離。另外,還有一部撿網球機器人,移動速度相當快速,造價只要十萬塊,而且已經相當成熟,不久之後,有可能量產,實際運用在球場檢球。

Wednesday, December 24, 2008

Google街景車台灣開跑

台北街頭若看見一台怪車,車頂架著一台「怪」攝影機,記得趕快跑到鏡頭前面多晃一下,這是Google的三六○度街景地圖車,拍攝的畫面將在明年三月底之後提供Google Phone手機使用,屆時全球Google Phone使用者都可以觀看到自己「不小心」的留影。

宏達電九月二十四日在紐約推出全球第一支可隨時上網、查看Google Map、Gmail、YouTube的手機Google Phone,最大賣點是可透過網路即時連結Google的三六○度的實景地圖,目前歐美共有二十三個主要城市,已完成實景地圖拍攝。

Google三六○度街景車進駐台灣,主要針對明年三月在台上市的Google Phone,屆時國人將跟歐美同步,利用手機即時觀看身歷實境的街景地圖。

Google這次在台灣拍攝三六○度街景地圖採用一台小轎車,車頂架上球型攝影機,跟在歐美拍攝用的廂型車不同,主要是考量台灣道路較窄,拍攝人員還計畫部分巷道以摩托車輔助。

Google台灣區總經理簡立峰表示,台灣街景拍攝將包括全主要城市和風景區,預計在半年內拍攝完成。

Tuesday, December 23, 2008

日本推出會洗碗的機器人 5年內問世

英國每日電訊報報導,日本新設計的家務助理機器人懂得先用水洗滌槽裏的碗碟,然後把它們排放好放入洗碗機,按鈕啟動洗碗程式。據了解,這個機器人可於5年內問世,

這個由東京大學和樂聲公司合作研製的多關節機器人,是特別為做家務而設計的一系列機器之一。

這個家務助理機器人安裝了18個精密的感應器,能夠用(手掌)緊握瓷器和食具,不會讓它們掉下或弄碎它們。

機器人的感應器還安裝了內置攝影機,能夠在拿起碗碟廚具放入洗碗機之前,確定放在洗滌槽裏的髒碗碟的形狀和大小。

研究人員希望製造出一個能夠在5分鐘內將一個四口之家的髒碗碟和廚房用具放入洗碗機的較小型機器人。

這個機器人可於5年內問世,研究人員還承諾將會研製能夠做其他家務,例如洗晾衣服的機器人等。

本則新聞由中廣新聞網提供

相關連結

Visit msnbc.com for Breaking News, World News, and News about the Economy

Monday, December 22, 2008

突破技術瓶頸/使用限制 3D臉部辨識技術躍居主流

| 新電子 2008 年 9 月號 270 期 |

| 文.鍾慶豐 彩色影像的分析與研究一直是影像處理領域的重頭戲,藉由對色彩資訊的掌握,其不變性將有助於對其應用有更深刻的了解。正如大家所熟知的,彩色影像分析的發展潛能很多,機器視覺(電腦視覺)、居家保全以及神經機械學(Cybernetics)更是熾手可熱的研究領域。本文將重點放在影像技術在居家保全上的變革,尤其是臉部辨識技術的發展與變遷,更是本次關心的焦點所在。 在發展臉部辨識系統技術往往會面臨三個瓶頸,首先是臉部影像資料庫的管理,其次為背景與前景環境複雜度的掌握,最後則是辨識大小的取樣限制。這些限制因子可以概分為內部因子與外部因子,對這些因子的掌握程度攸關新技術能否被大眾接受。 http://www.mem.com.tw/technologyexploring_content.asp?sn=0809170007 |

Friday, December 12, 2008

臺科大機器人劇團

【記者林永富報導】眉毛挑動,張開嘴巴唱歌,您沒有看錯,這是台科大機器人,會走路、打鼓、更進一步會看簡譜唱歌、畫畫、說相聲,有趣的是,以矽膠材質做成的仿真人臉孔,可以變化表情。「機器人劇場表演只是我們完成的第一步」,台科大機器人研究中心主任林其禹指出,未來要讓機器人更多才藝就像真的劇團表演。台科大機器人研究中心團隊今(11)日展出四具機器人,其中仿真人製作的一男一女機器人Thomas和Janet,可以看簡譜唱歌、說相聲,臉部會表現出哭笑、驚訝等表情,是智慧型機器人的大突破。另兩具則是會素描、畫畫的Pica,取其畢卡索才華為名;Ringo 則是以披頭四的鼓手同名,會打爵士鼓的音樂機器人。三年多來機器人研究中心團隊,在經費並不充裕的情況之下,幾乎從無到有,機械系博士班邱逸斌、鄭立傑說,「我們從一個一個零件組合,到整個跟人一樣高的機器人站在面前,中間經過太多太多失敗挫折」。博士班曾昌國說,光是研究機器人的臉部表情,就花了三年,不斷改進之下,現在才有像人一樣變化表情。碩士班林冠宏表示,「就在它能兩腳落地走路跨出第一步,大家都感動的都快哭了」。林其禹指出,這四具機器人三年來總經費大約四千多萬元,其中有國科會、教育部的補助款,以及學校預算編列,光是硬體製作就去掉三千萬,可以說在最節省的情況下研發,非常難得。他說,智慧型機器人日本及南韓已投入研究多年,而且經費充裕,所以我們三年前開始時,就定調在可以快速產業化的價值項目技術,因此選定劇場表演機器人來研發。整個團隊分為不同項目分工,機械系硬體研發、資工系鍾國亮教授在音樂簡譜辨識研發、古鴻炎教授在歌聲合成研發上,都花了很大的心力。台科大將在本月27日下午四點,完整演出機器人劇場表演會,是全世界第一場由大型仿真人臉雙足人形機器人和雙輪機器人,共同演出的表演綜藝節目。除一般民眾之外,也將邀請100位育幼院院童一起觀賞。

Thursday, December 11, 2008

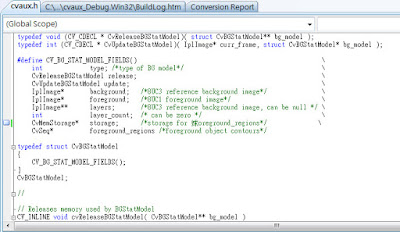

Steps of porting the OpenCV application to 1.1pre1

- Download the latest version OpenCv 1.1Pre1.

- Open the "OpenCV\_make" and select the opencv.dsw

- Select the cv, cvaux,... and use the "Win32 release", "Win 32 Debug" respectively.

- According the compiling error, delete "*.pdb" under the "OpenCV\bin".

- Select the cvaux use the "Win32 release", "Win 32 Debug" respectively. The error of "error C2039: 'foreground_regions' : is not a member of 'CvFGDStatModel'" will be shown.

- Select the "OpenCV\cvaux\include\cvaux.h" and edit the

- CvMemStorage* storage; /*storage for oreground_regions?/ \

- CvMemStorage* storage; /*storage for oreground_regions*/ \

- CvMemStorage* storage; /*storage for oreground_regions?/ \

- Save and compile again.

- Select cvSample, cvtest, highGui,.. and compile "Win32 release", "Win 32 Debug"respectively.

- Try compile the existed application and require to remove the ""C:\Program Files\OpenCV\lib\cvcam.lib" and "C:\Program Files\OpenCV\lib\cvcamd.lib" from the VC project settings.

- Remove the ffopencv.dll at "windows\system32" since no working at "cvCreateVideoWriter_Win32".

- cvPuttext with the inverse vertical setting and need to modify.

Wednesday, December 10, 2008

新研發機器人準備跟服務犬搶飯碗

Tuesday, December 09, 2008

自動化光學檢測人才培育專題講座

教育部顧問室 產業設備系統設計人才培育先導型計畫

一、講座目的:

二、主辦單位:

三、地 點: 國立台北科技大學 台北市忠孝東路三段一號

第六教學大樓(科技大樓) 教室:526

- 2008/12/11, 18 : 30~21 : 40

- 2008/12/25, 18 : 30~21 : 40

Friday, November 28, 2008

低廉智慧型載具 By 正修科大

經三年研發,高雄縣正修科技大學與陸軍官校完成「智慧型載具」(機器人),造價較外國低廉,且可擴充功能,成為軍事、化學災害、災區生命探測的利器。 這輛總重 110公斤的機器人以電動馬達驅動履帶行走,裝置機械手臂。電子系助理教授張法憲表示,機器人以無線遙控,加裝監視器,履帶讓機器人可行走在各種路面或爬坡,有效遙控距離 800公尺,機械手臂可夾帶30公斤的物品,可移除爆裂物;可加裝偵測系統,成為災區生命探測、掃除地雷、危險彈藥搬運等工具,甚至職災時將受傷民眾拖離災區;如加裝太陽能板與蓄電池、「主動式保全系統」,可成為全天候保全巡護系統。

張法憲表示,這部機器人造價新台幣 200多萬元,比軍方、警方自國外購置移除爆裂物機器人約新台幣700 萬元低廉。

Wednesday, October 22, 2008

創新應用整合案例-視覺型火災偵測系統三秒內緊急通報

Wednesday, October 08, 2008

Tuesday, September 30, 2008

自行車機器人即將上路

Friday, September 26, 2008

會騎獨輪車的機器人小妹妹亮相

日本業者村田製造(Murata Manufacturing),開發出了一款名為「村田小妹(Murata Girl)」、騎著獨輪車的機器人;這款機器人配備了陀螺儀感測器、藍牙,以及超音波等功能,能垂直站立或是四處移動。

這款機器人採用了多個村田自有的元件,包括用以在電路儲存電力的電容器、控制運動的感測器,以及跟外接交換資訊的通訊模組。該公司表示,由於有感於日本兒童對於科學的興趣日漸低落,該公司過去曾推出過一款騎著腳踏車的「村田頑童(Murata Boy)」機器人,並主動聯繫各學校提供教育機會,藉由展示該機器人讓學童們知道科學有多麼好玩。

新誕生的「村田小妹」外觀與個性是由一個女性成員組成的團隊負責設計,得克服機器人騎著獨輪車維持平衡與移動的挑戰,並讓它利用一顆超音波感測器來與週遭物體保持距離,同時透過一具實況攝影機來傳送移動的影像。

嬌小的「村田小妹」高50公分、體重5公斤,使用兩個陀螺儀感測器發出的訊號來偵測機器人的傾斜角度,以協助控制獨輪車該前進或後退;在其軀幹部並裝置了一個飛輪(fly wheel),用以監測機器人的兩側,好維持左右平衡。

「村田小妹」身上的一對收/發超音波感測器,能透過訊號發出與彈回的時間,來偵測自己與障礙物間的距離。外界指令以及各種資料的接收/發送,則是透過行動終端設備與PC,使用2.45GHz無線頻段來傳遞。它還配備多款村田自家的通用電子元件,包括晶片陶瓷電容、Ceralock陶瓷振盪器、測溫度用的NTC電熱感測器、電位計,以及雜訊抑制濾波器等。

村田製造並提供了“非常多”有關「村田小妹」的詳細資料,說她是「村田頑童」的小堂妹,生日是9月23日,出生於日本滋賀縣,目前唸幼稚園中班,而個性是「天生好動又怕羞」。

Thursday, September 25, 2008

Monday, July 14, 2008

Using the KMPlayer to convert the asf/wmv format to vfw avi.

Wednesday, May 28, 2008

Writing a Transform Filter

http://www.ifp.uiuc.edu/~chenyq/research/Utils/DShowFilterWiz/DShowFilterWiz.html

Wednesday, May 14, 2008

Monday, May 05, 2008

高速視覺技術及三指機械手介紹

大多數的智慧型機器人均具備有許多的環境感測技術,例如使用超音波或者雷射來進行障礙物偵測,使用微波或者GPS 技術來進行定位以及利用視覺技術來分辨目標物等;隨著機器人產品的發展愈趨複雜,因此對於機器人互動技術的規格要求也愈來愈高。高速視覺技術已經被視為未 來應用在機器人上最主要的環境感測技術,透過高速視覺技術可以快速地協助機器人定出空間位置、瞭解周遭環境與物體以及即時監控環境當中之異常事件等。

在本期文章我們將深入介紹由日本東京大學石川正俊教授所領導的研究團隊,針對目前廣泛應用在服務用以及產業用機器人之高速視覺技術的研究成果與由HarmonicDrive所發展的輕量型高速三指機械手,以及兩者結合之應用實例。

何謂高速視覺?

日本科學未來館當中展示了一組智慧型的機械手,該手臂搭配一雙眼睛就可以快速抓住任何丟向它的球或其他形狀之物體(如圖1)。普榮獲2007年機器人大獎賽冠軍的裝箱抓取機械手臂(如圖2),透過三支機械手臂可以快速的抓取於輸送帶中移動的任何商品,並精準地放置於包裝箱中。

此外,Fanuc以及Denson等傳統機械手臂生產大廠不約而同的在2007年日本機器人展當中推出可以附加於機械手臂上之高速視覺模組,使傳統機械手臂的應用因為加入的視覺技術而更有智慧,未來的機械手臂將可自行判斷物體形狀、大小以及外觀,然後自動的抓取物品,搬移到目標位置。

圖1 結合高速視覺模組之機械手(展示於日本科學未來館中)

圖2 抓取裝箱機械手臂

高速視覺技術(High Speed Vision Technology)就是這一隻手(手臂)的眼睛,透過每一秒鐘高達1000張圖片的抓取與高速的運算分析,就可以快速的掌握到移動或者靜止的分散物體,分析它的移動路徑、形狀以及大小,進而判斷其立體空間座標而驅動運動機構去作抓取與搬運動作。

高速視覺介紹

影像處理技術必須透過感光、影像傳輸、成像、合成等過程,並經由後端處理器進行影像壓縮與檔案後處理作業,除了資料的傳輸量大之外,還需要大量的處理器運算資源做影像處理。高速影像技術乃是利用FPGA(Field Programmable Gate Array)做為核心控制處理架構並結合高速傳輸介面,以及FPGA的高速運算能力,可重複規劃等數位訊號處理之優越性,配合動態影像的取得以及同步動態隨機存取記憶體(Synchronous Dynamic Ram,SDRAM)所發展而成。

日本東京大學石川正俊教授針對機器人的環境感測技術進行許多研究,其中最重要的研究成果便是發展「高速視覺晶片」(High Speed Vision Chip),將影像感測模組與數位處理元件整合於一片積體電路當中,同時利用第二級FPGA處理器架構(Secondary FPGA)強化了原本單一晶片的運算限制,並提供平行計算演算法,使得多的處理器得以同時運算大幅提昇運算技術能力,也因此得以每一秒鐘擷取超過1000張影像之能力。

|

圖3 高速視覺晶片 |

圖4 高速視覺晶片架構 |

傳統的影像處理速度一般都只有到30~100 frames/sec,處理速度雖不夠快,但用在一般3C產品上已經足夠;然而若要將視覺技術應用於機器人的感測上,若影像擷取速度不夠快的話,對於快速 移動的物體並無法及時偵測到,也無法瞭解到其移動路徑,會因而降低機器人對外在環境之反應力。石川教授的高速視覺晶片,因可以在每一秒鐘擷取高達1000 張影像(這樣的速度已經超越人類眼睛),因此透過影像與影像之間的分析與比對之後,便可即時掌握物體的移動、空間的辨識等。

機械手介紹

本次所參觀之東京大學石川實驗室當中,在結合高速視覺技術部分應用到了許多由HarmonicDrive所開發的三指擬人機械手(如圖5)。該機械手每一手指具有兩個自由度,可以作兩個關節的彎曲,並且在手指與手指之間還有一個自由度可以作兩個手指的開合動作。

圖5 HarmonicDrive三指機械手

HarmonicDrive在手指部分主要以兩種制動器做為關節驅動部分,包含RSF-38-100以及RSF-5A-50等,兩者分別使用1/100以及1/50的減速比提升其輸出扭力,末端最大出力為0.3Nm(牛頓米)。

圖6 Harmonic Drive手指模組機構示意圖

HarmonicDrive三指機械手機構不論在轉速或扭力的表現上,已經超越目前業界水準,且整隻手的應用涵蓋範圍也很廣,包括物品夾持、簡易工具操作等,在正式的實驗當中,使用HarmonicDrive機構手已經可以做出以下動作:

目前大部分的擬人機器人多採用人工肌肉來完成手部動作,其壽命有一定限制,且在速度以及扭力表現上均還無法達到與人相同之地步;因此,如HarmonicDrive所開發三指擬人機械手已經可以將傳統機械手的速度跟扭力拉升至與人相同,但在關節自由度的表現上,許多地方仍以同動方式為主,此外在指節末端關節處也無實現。因此,嚴格來說HarmonicDrive之三指機械手,仍無法與人類的手掌相比,因其對於更靈活之動作要求,目前是無法達到的。

目前日本已有多所大學投入研發機械手計畫,包含本次在日本展覽當中看到由東京大學以線驅動方式開發之五指機械手;以及由產總研(AIST)所研發應用於HRP-3P之四指17個自由度之機械手,已經可以將機械手縮小到180mm,並達到15Nm之出力。

|

圖7 線驅動機械手 |

圖8 AIST全馬達驅動機械手 |

除了日本外,各國在機械手的研發工作上一直都有成果,以下列出具代表性之研發成果:

|

| DLR(德國宇航中心) II研發出四指擬人靈巧抓取的作業系統,每手指結構相同,各有4個關節和3自由度,另外在手掌內有一自由度,讓機器手能穩定的抓取和操作調整。DLR II機器手具有開關抽屜、操作設備以及使用工具等動作。 |

|

| 英國Shadow研發出24自由度五指的機器手,採用人工肌肉方式驅動,重量大約3.Kg,Shadow機器手在指尖上裝有觸碰感測,允許在柔軟或脆弱的物體上使用。 |

|

| 日本Squse公司設計的機器手用21條人工肌肉牽動關節,能像人手一樣抓取物品及與人握手,它甚至能勝任包裝生雞蛋這樣的細緻工作。 |

高速視覺應用實例

石川教授除了發展高速視覺技術之外,並利用此技術發展了相關應用技術,包含高速物體追蹤系統(High Speed Catching System)、目標物統計(Target Counting)、即時多目標物判斷(High Speed Based Moment Analysis of Numerous Object)、轉速測量(Rotation Measurement)、微細世界之視覺回饋系統(Microscopic Visual Feedback)等。

|

| 高速追蹤系統可以透過高速視覺技術來追蹤移動中之物體,並利用機械手將物體抓取到位。此外,利用機械手臂做棒球打擊等應用也屬於相同原理。 |

|

| 利用特徵分析與移動追蹤技術,可以在一個影像上分辨出多個目標物,並且同時偵測這些目標物之狀態改變。 |

|

| 利用高速視覺技術可以對移動中之物體做數量統計。譬如一盤流沙,以瀑布方式傾瀉而下經由高速視覺之判斷可以精準無誤地統計出該流沙有多少沙粒。 |

|

| 利用高速視覺技術針對一轉動之球面物品進行特徵分析,並藉由此特徵進一步分析出其轉速。 |

|

| 結合顯微鏡技術以及高速視覺技術,可以觀察到微細世界之狀態。 |

石川教授所研發之高速影像處?系統的IC晶片,未?希望朝?快速及?有智慧性的方向研發,在應用上未來可朝向高速檢測儀器、生技醫?手術輔助、道?影像攝影、賽?終點判定、視覺介面、追蹤辨識系統等。

此外,在產業應用上也已經有多款服務型與產業用機器人結合視覺技術,在2007日本機器人展當中已經有許多產業應用實例出現,包含有:

|

| 日本機械手臂大廠Fanuc於2007年正式推出結合視覺辨識模組之機械手臂,透過視覺技術,機械手臂可以在特定區域抓取散落之物品,而無須預先排定物品位置。並且可以透過視覺技術偵測物體形狀與大小以決定抓取方式,提供機械手臂更有彈性之應用。 |

|

| Denson機械手臂結合三組CCD,可以呈現出多個目標物體之3D立體圖像,並回饋給機械手臂進行搬移。 |

|

| 日本生產技術株式會社利用視覺技術賦予機器人玩魔術方塊之技巧,該機器人可以透過視覺技術判斷目前方塊狀況,並進行推演然後透過兩隻機械手完成魔術方塊遊戲。 |

|

| 乒乓球機器人可以跟人一起打乒乓球。該款機器人利用視覺技術來追蹤乒乓球之移動路徑,然後在落點後將球回擊。 |

高速視覺之未來發展

在本次的參訪當中,石川教授的高速視覺技術已經證明可以提供機器人或應用載具基本的環境感測功能,達到物體識別、移動追蹤、立體視覺等,且高速視覺技術在成本與速度上已經超越傳統的雷射掃描器,因此在近幾年吸引許多廠商投入研發。

然而,視覺在感測的同時容易受到燈光之影響,而影響到判斷的精確度,進而造成誤判等嚴重疏失,而會有安全上之疑慮,未來必須倚賴更精密與更高速之變焦技術來解決此問題。

再 者,是否未來機器人僅需使用視覺技術即可取代目前所使用的所有感測技術,仍有許多爭議。一方面視覺技術在感測精度上會隨著距離而遞減,再者對於許多障礙物 的偵測,單靠視覺技術仍無法做出最正確的判斷,因此短時間內雖可見到視覺技術應用於機器人上,但仍須要結合其他感測技術如超音波、雷射等。

此外,透過視覺技術來模擬生物的眼睛,亦為視覺技術發展的主軸,但在實際的產品上,仍無法達到非常理想的跨距,以Point Gray目前所推出的3D視覺模組系統(Stereo Vision),跨距至少要12cm才能夠做出3D立體成像,對於小型化的機器人商品因無法使用過寬的跨距,有關於跨距問題在未來仍必須在技術上突破。

圖9 Point Gray立體視覺模組

結語

本期我們為各位介紹關於東京大學石川正俊教授所主持之高速視覺技術,並利用高速視覺技術所發展之相關應用。在近兩年當中,已經有愈來愈多的廠商結合視覺技術來強化本身原有產品之應用,尤以產業用機器人為大宗。隨著IC處理器製程技術更加進步之際,也將會推動視覺技術更往前邁進,並可將視覺技術結合其他感測技術後提供機器人產品更加敏銳之環境感測能力。

在下一期文章當中,將介紹日本產業技術總合研究所(AIST)的共通性雙足機器人開發平台HRP-3P與相關機器人之研發成果。

http://www.robotworld.org.tw/index.htm?pid=10&News_ID=1557

Tuesday, April 22, 2008

The C Programmers Guide to Verilog

In the near future, embedded systems designers will be able to use hardware and software interchangeably depending on which best solves a specific design problem. Up until now, the barriers were so high for software engineers who wanted to learn hardware design that few explored the space. The barrier is crumbling because of the similarity between hardware description languages and programming languages. Also, several reasonably low-cost demonstration boards are available that include a field-programmable gate array (FPGA), a microprocessor, and tools that even a software developer can use to learn hardware design.

This article offers an example of this new design process using an FPGA. We'll look at how to implement pulse width modulation (PWM) in software and then turn the design into a logic block that can run from an FPGA and be controlled via software using a memory-mapped I/O interface. You can do everything in this article with the FPGA development kits that are available today from major FPGA manufacturers.

Hardware-software divide Several things have changed that make it easier for software engineers to participate in hardware design. Both hardware and software modules are now designed using programming languages. As you know, C is the lingua franca of embedded software design. On the hardware side, Verilog is often the popular choice (though both VHDL and Verilog are popular). The syntax and structure of Verilog is similar to that of the C programming language, as the examples in this article will illustrate.

At the same time, hardware is getting easier to update and change. It used to be that software could be changed simply by downloading a new executable image while hardware could not. That's no longer entirely true. Just as a software developer can make a quick edit, recompile, and then download the new code into memory, hardware designers using programmable logic have a similar capability. Programmable logic changes the method for designing embedded systems by enabling you to change the hardware as easily as the software. In other words, it affords you the flexibility during design and debugging to choose the best way to handle these tasks—either in software or hardware.

Tools are available from FPGA vendors that enable a designer with a little knowledge of hardware to develop an embedded system for programmable logic, such as an FPGA. For example, the SOPC Builder from Altera (my employer) enables system designers to select and configure peripherals from an existing library as well as add user logic to create and tie peripherals together. With programmable logic and some hardware knowledge, software engineers can take advantage of the benefits of hardware to improve their systems.

PWM software A PWM controller produces a stream of pulses like those shown in Figure 1. Usually the period and pulse width are specified. The duty cycle, or on time, is defined as the ratio of the pulse width to the period. Figure 1 shows a PWM waveform of about 33% duty cycle.

Figure 1: A PWM waveform

Figure 1: A PWM waveform

PWM is used in many applications, most frequently to control analog circuitry. Because the digital signal varies continuously at a relatively fast rate (depending on the period, of course), the resulting signal will have an average voltage value, which can be used to control an analog device. For example, if a stream of PWM pulses is sent to a motor, it will turn at a rate proportional to the duty cycle (from 0% to 100%). If the duty cycle is increased, the motor will turn faster; likewise, if the duty cycle is decreased the motor will slow.

For more information about PWM, consult Michael Barr's Beginner's Corner article "Introduction to Pulse Width Modulation" (September 2001, p. 103).

Generally speaking, PWM is implemented in hardware because the output signal must be continuously updated—going high from the start of each period for the proper time, then low for the remainder of the period. Software usually just handles the selection of the period and duty cycle and perhaps occasionally making changes to the duty cycle, to effect a behavioral change in whatever is attached to the PWM output.

There's no reason, however, that software couldn't be used to implement PWM, say by bit-banging a spare output pin. Writing such a PWM controller in software is a relatively trivial task and helps illustrate what we will do in Verilog shortly. Listing 1 shows the C code for PWM.

Listing 1: A bit-banging PWM controller implemented entirely in software

void pwmTask(uint32_t pulse_width, uint32_t period) { uint32_t time_on = pulse_width; uint32_t time_off = period - pulse_width;while (1) { pwm_output = 1; sleep(time_on); pwm_output = 0; sleep(time_off); } }

Based on the pulse_width and period arguments to this function, the PWM calculates the amount of time the output will be high and low. The infinite loop then sets the output pin high, waits for time_on time units to elapse, sets the output low, waits for time_off, and then repeats the cycle for the next period.

Verilog Listing 2 shows a simple Verilog module implementing an 8-bit wide register with an asynchronous reset. The input of the register, in, is assigned to the output, out, upon the rising edge of the clock, unless the falling edge of the clr_n reset signal occurs (in which case the output is assigned a value of 0).

Listing 2: Verilog module for a register with asynchronous reset

module simple_register(in, out, clr_n, clk, a);

| // port declarations | ||

| input input input [7:0] input output [7:0] | clr_n; clk; in; a; out; | |

| // signal declarations | ||

| reg [7:0] wire | out; a; | |

| // implement a register with asynchronous clear always @(posedge clk or negedge clr_n) begin | |||

| if (clr_n == 0) // could also be written if (!clr_n) | |||

| out <= 0; | |||

| else | |||

| out <= in; | |||

| end

// continuous assignment assign a = !out[0]; | |||

Glancing at the Verilog listing, you should notice several similarities to the C programming language. A semicolon is used to end each statement and the comment delimiters are the same (both /* */ and // are recognized). An == operator is also used to test equality. Verilog's if..then..else is similar to that of C, except that the keywords begin and end are used instead of curly braces. In fact, the begin and end keywords are optional for single-statement blocks, just like C's curly braces. Both Verilog and C are case sensitive as well.

Of course, one key difference between hardware and software is how they "run." A hardware design consists of many elements all running in parallel. Once the device is powered on, every element of the hardware is always executing. Depending on the control logic and the data input, of course, some elements of the device may not change their outputs. However, they're always "running."

In contrast, only one small portion of an entire software design (even one with multiple software tasks defined) is being executed at any one time. If there's just one processor, only one instruction is actually being executed at a time. The rest of the software can be considered dormant, unlike the rest of the hardware. Variables may exist with a valid value, but most of the time they're not involved in any processing.

This difference in behavior translates to differences in the way we program hardware and software code. Software is executed serially, so that each line of code is executed only after the line before it is complete (except for nonlinearities on interrupts or at the behest of an operating system).

A Verilog module starts with the module keyword followed by the name of the module and the port list, which is a list of the names of all the inputs and outputs of the module. The next section contains the port declarations. Note that all of the input and outputs appear in both the port list in the first line of the module and in the port declarations section.

In Verilog, two types of internal signals are widely used: reg and wire. These types differ in function. All parts have a signal by the same name implicitly declared as a wire. Therefore, the line declaring a as a wire is not necessary. A reg will hold the last assigned value so it doesn't need to be driven at all times. Signals of type wire are used for asynchronous logic and sometimes to connect signals. Because a reg holds the last value driven, inputs cannot be declared as a reg. An input can change at any time asynchronous to any event in the Verilog module. The main difference, however, is that signals of type reg can only be assigned a value in procedural blocks (discussed later) while signals of type wire can only be assigned a value outside of procedural blocks. Both signal types can appear on the right-hand side of the assignment operator inside or outside of any procedural block.

It's important to understand that using the reg keyword doesn't necessarily mean the compiler will create a register. The code in Listing 2 has one internal signal of type reg that's 8 bits wide and called out. This module infers a register because of the way the always block (a type of procedural block) is written. Notice that the signal a is a wire and thus is assigned a value only in the continuous assignment statement while out, a reg, is assigned a value only in the always block.

An always block is a type of procedural block used to update signals only when something changes. The group of expressions inside the parentheses of the always statement is called the sensitivity list; it's of the form:

(expression or expression ...)

The code inside the always block is executed whenever any expression in its sensitivity list is true. The Verilog keywords for rising edge and falling edge are posedge and negedge, respectively. These are often used in sensitivity lists. In the example shown, if the rising edge of the clk signal or the falling edge of the clr_n signal occurs, the statements inside the always block will be executed.

To infer a register, the output should be updated on the rising edge of the clock (falling edge would work too, but the rising edge is more common). Adding negedge clr_n makes the register reset upon the falling edge of the clr_n signal. Not all sensitivity lists will contain the keywords posedge or negedge, though, so there won't always be an actual register in the resulting hardware.

Inside the always block, the first statement asks if the falling edge of the clr_n signal occurred. If it did, then the next line of code sets out to 0. These lines of code implement the asynchronous reset portion of the register. If the conditional statement were:

if (negedge clr_n and clk == 1)

then it would be a synchronous reset that depends on the clock.

You may have noticed that the assignment operators inside the always block are different from the one used in the continuous assignment statement that begins with the assign keyword. The <= operator is used for nonblocking assignments while the = operator is used for blocking assignments.

In a group of blocking assignments, the first assignment is evaluated and assigned before the next blocking assignment is executed. This process is just like C's serial execution of statements. With nonblocking assignments, though, the right hand side of all assignments are evaluated and assigned simultaneously. Continuous assignment statements must use the blocking assignment (the compiler will give an error otherwise).

To make the code less prone to errors, it's recommended that you use nonblocking assignments for all assignments in an always block with sequential logic (for example, logic that you want implemented as registers). Most always blocks should use nonblocking assignment statements. If the always block has all combinatorial logic, then you'll want to use blocking assignments.

PWM hardware One of the first tasks when writing a memory-mapped hardware module is to decide what the register map will look like from the software perspective. In the case of PWM, you want to be able to set the period and pulse width in software. In hardware, making a counter that counts system clock cycles is easy. Therefore, there will be two registers, the pulse_width and the period, both measured in clock cycles. Table 1 shows the register map for the PWM.

Table 1: Register map for PWM

| Address | Name | Width | Description |

| 0 | period | 32 bits | Number of clock cycles for one period |

| 1 | pulse_width | 32 bits | Number of clock cycles the output will be high |

Next, choose the ports for the PWM, most of which are already determined based on the bus architecture. Table 2 has a brief description of the signals for a generic memory-mapped PWM. Note that a popular naming convention for active low signals is to add an "_n" to the signal name, which are fairly common for control signals. The signals write_n, and clr_n in Table 2 are active low (falling-edge triggered) signals.

Table 2: Ports for PWM

| Signal Name | Direction | Description |

| clk | Input | System clock |

| write_data[31:0] | Input | Write data (for registers in register map) |

| cs | Input | Chip select |

| write_n | Input | Write enable, active low |

| addr | Input | Address (to access registers in register map) |

| clr_n | Input | Clear, active low |

| read_data[31:0] | Output | Read data output |

| pwm_out | Output | PWM output |

Now that we have defined the interface of the hardware module, we can start writing the Verilog code. An example implementation is shown in Listing 3.

Listing 3: PWM hardware implementation in Verilog

| module pwm (clk, write_data, cs, write_n, addr, clr_n, read_data, pwm_out); | ||||||

| // port declarations | ||||||

| input input [31:0] input input input input output [31:0] output | clk; write_data; cs; write_n; addr; clr_n; read_data; pwm_out; | |||||

| // signal declarations | ||||||

| reg [31:0] reg [31:0] reg [31:0] reg reg [31:0] wire | period; pulse_width; counter; off; read_data; period_en, pulse_width_en; // write enables | |||||

| // Define contents of period and pulse_width registers // including write access for these registers always @(posedge clk or negedge clr_n) begin | ||||||

| if (clr_n == 0) | ||||||

| begin | ||||||

| period <= 32'h 00000000; pulse_width <= 32'h 00000000; | ||||||

| end | ||||||

| else | ||||||

| begin | ||||||

| if (period_en) | ||||||

| period <= write_data[31:0]; | ||||||

| else | ||||||

| period <= period; | ||||||

| if (pulse_width_en) | ||||||

| pulse_width <= write_data[31:0]; | ||||||

| else | ||||||

| pulse_width <= pulse_width; | ||||||

| end | ||||||

| end | ||||||

| // read access for period and pulse_width registers always @(addr or period or pulse_width) | ||||||

| if (addr == 0) | ||||||

| read_data = period; | ||||||

| else | ||||||

| read_data = pulse_width; | ||||||

| // counter which continually counts up to period always @(posedge clk or negedge clr_n) begin | ||||||

| if (clr_n == 0) | ||||||

| counter <= 0; | ||||||

| else if (counter >= period - 1) // count from 0 to (period-1) | ||||||

| counter <= 0; | ||||||

| else | ||||||

| counter <= counter + 1; | ||||||

| end // Turns output on while counter is less than pulse_width; otherwise // turns output off. // !off is connected to PWM output always @(posedge clk or negedge clr_n) begin | ||||||

| if (clr_n == 0) | ||||||

| off <= 0; | ||||||

| else | ||||||

| if (counter >= pulse_width) | ||||||

| off <= 1; | ||||||

| else | ||||||

| if (counter == 0) | ||||||

| off <= 0; | ||||||

| else | ||||||

| off <= off; | ||||||

| end | ||||||

| // write enable signals for writing to period and pulse_width registers

assign period_en = cs & !write_n & !addr;

assign pulse_width_en = cs & !write_n & addr;

// PWM output assign pwm_out = !off; | ||||||

| endmodule | ||||||

The first signals are the port declarations, which were described in Table 2. After the port declarations come the internal signal declarations. The memory-mapped registers that make up the software interface to control the PWM are declared reg. The code allows for only 32-bit accesses to these memory-mapped registers. If you need 8-bit or 16-bit access, then you would split the registers into four 8-bit registers and add logic for byte enable signals. The Verilog code to implement this is straightforward. All the signals with assigned values in the always blocks are also declared reg. The signals declared wire are the write enables for the registers period and pulse_width. These signals are assigned values using continuous assignment statements.

The rest of the listing contains the actual code. There are four always blocks and several assignment statements at the end. Each always block describes the behavior for one signal or a group of signals that have the same basic behavior (in other words, use the same control logic). This is a clean way of writing Verilog code that keeps the code readable and less prone to errors. All of the always blocks have reset logic that sets the signal(s) to 0 when the clr_n signal is asserted (set to 0). While not strictly necessary, this is a good design practice so that every signal has a known value upon reset.

The first always block describes the behavior of the registers in the register map. The value of the write_data register is written into the period or pulse_width register if the appropriate enable signal is asserted. That is the only way to change the values of either register. The write enable signals are defined in the continuous assignment statements at the bottom of the file. The write enables for the period and pulse_width registers are asserted when the main write enable signal and the chip select signal are asserted; the addr bit should be set to 0 for period and 1 for pulse_width.

The second always block defines reading the registers in the register map. The period register will be at the base address of the peripheral, and the pulse_width register will be at the next 32-bit word.

The third and fourth always blocks work together to determine the output of the PWM. The third always block implements a counter that continually counts up to the value in the period register, resets to 0, and begins counting again. The fourth always block compares this counter value to the pulse_width register. While the counter value is less than the pulse_width, the PWM output is kept high; otherwise it's set low.

One thing to keep in mind is that every signal must have a defined value under all conditions. This goes back to one of the fundamental behaviors of hardware—it's always running. For example, in the last always block (the one that describes the off signal) the last line of code assigns off to itself. This may seem strange at first, but without this line, the value of off would be undefined for that case. An easy way to keep track of this is to make sure that every time a signal is assigned a value in an if statement, it is assigned a value in the corresponding else statement as well.

Software access Now that the hardware is complete, the PWM can be controlled via software using the registers in the register map. You can use a simple data structure along with a pointer to connect to the registers in the PWM.

typedef volatile struct { uint32_t period; uint32_t pulse_width;} PWM;

For example, the PWM could be hooked to an LED. A variable called pLED of type PWM * could be initialized to point to the PWM base address. This abstracts the hardware into a data structure. Writing to pLED->period will set or change the period. Writing to pLED->pulse_width will change the duty cycle and cause the brightness of the LED to increase or decrease. If a blinking LED is desired, the period need only be lengthened, so that the human eye perceives the on and off periods as distinct.

The Verilog PWM implementation shown in Listing 3 was tested as a peripheral for Altera's Nios processor system and accessed via software using a C struct like the one I previously described. Altera's SOPC Builder creates macros that facilitate performing co-simulation in ModelSim, a hardware simulator from Mentor Graphics. Using the ModelSim simulator, the behavior of the PWM signals, along with the rest of the system's signals, can be observed while the system is executing C code.

Listing 4 shows the C code that was used to generate the waveform in Figure 2. The waveform shows the behavior of the pertinent PWM signals. The C code writes to the PWM registers to create a PWM output with a period of five cycles and a pulse width of four. Notice that at the beginning of the waveform, the cs and wr_n signals are asserted twice since we're writing to both the period and pulse_width registers. (The address signal is low when writing to the period register and high when writing to the pulse_width register.)

Listing 4 Test software used to produce waveforms in Figure 2

void main(void) { PWM * const pLED = ...pLED->period = 5; pLED->pulse_width = 4;

asm("nop"); asm("nop"); asm("nop");

pLED->pulse_width = 2; }

Figure 2: Waveform for software-controlled PWM hardware

Figure 2: Waveform for software-controlled PWM hardware

After the new values have been written to the registers, the pwm_output signal begins to reflect the change. Then, just to add some delay so we can see the output, some NOP instructions are executed by the C code. Finally, the pulse width is changed to two cycles, and the PWM waveform changes accordingly while still having a period of five cycles.

Best of both worlds Part of architecting an embedded system is partitioning the system into hardware and software modules to take advantage of the benefits of each. As development tools evolve, interchanging software and hardware modules is becoming more transparent to the designer.

Once you understand the concepts discussed in this article, you'll have the knowledge to develop hardware on an FPGA that can be hooked up as a memory-mapped peripheral in a microprocessor system and interfaced by simply writing software. Because certain algorithms run much faster in hardware, converting an algorithm from software to hardware may greatly increase system performance. Known as hardware acceleration, the ability to do this is key to using configurable processors implemented effectively in programmable logic. At long last, even a software engineer has the power to improve system performance and efficiency through hardware acceleration.

Lara Simsic is an applications engineer at Altera. She has developed embedded hardware and software for five years and has an EE degree from the University of Dayton. Contact her at lsimsic@altera.com.